ASPLOS'20 - Session 13A - HMC: Model Checking for Hardware Memory Models

ASPLOS'20 - Session 13A - HMC: Model Checking for Hardware Memory ModelsПодробнее

How to Extract SRAM ModelsПодробнее

Model Checking for Weakly Consistent LibrariesПодробнее

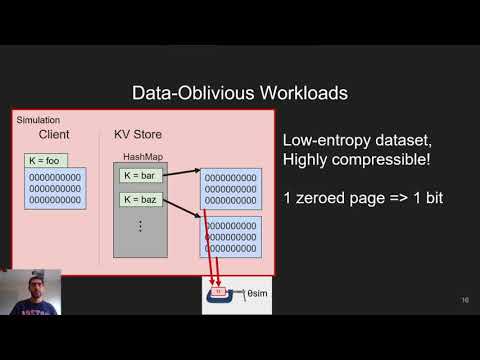

ASPLOS'20 - Session 4A - 0sim: Preparing System Software for a World with Terabyte-scale MemoriesПодробнее

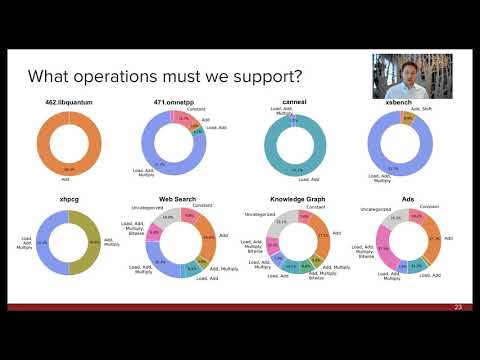

ASPLOS'20 - Session 6B - Classifying Memory Access Patterns for PrefetchingПодробнее

ASPLOS'20 - Session 13A - Cross-Failure Bug Detection in Persistent Memory ProgramsПодробнее

[OOPSLA] Model Checking for a Multi-Execution Memory ModelПодробнее

![[OOPSLA] Model Checking for a Multi-Execution Memory Model](https://img.youtube.com/vi/0qSRTwUi1ts/0.jpg)

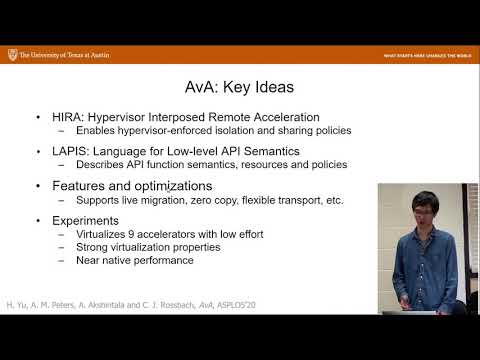

ASPLOS'20 - Session 9B - AvA: Accelerated Virtualization of AcceleratorsПодробнее

ASPLOS'20 - Session 11A - MERR: Improving Security of Persistent Memory Objects via Efficient MemoryПодробнее

ASPLOS'22 - Session 4B - Clio: A Hardware-Software Co-Designed Disaggregated Memory SystemПодробнее

ASPLOS'20 - Session 4B - Durable Transactional Memory Can Scale with TimestoneПодробнее

ASPLOS'20 - Session 3B - FlexAmata: A Universal and Efficient Adaption of Applications to SpatialПодробнее

ASPLOS'20 - Session 9A - MOD: Minimally Ordered Durable Datastructures for Persistent MemoryПодробнее

[PLARCH23] Design for Hardware Memory Model VerificationПодробнее

![[PLARCH23] Design for Hardware Memory Model Verification](https://img.youtube.com/vi/I_J4kor6WjI/0.jpg)

MIPSfpga - Module 13: CachesПодробнее

Loading the core memory diagnostic test from paper tape on Univac 1219B military mainframeПодробнее

Making Weak Memory Models FairПодробнее