using RAM ip in Quartus, with Initial Data

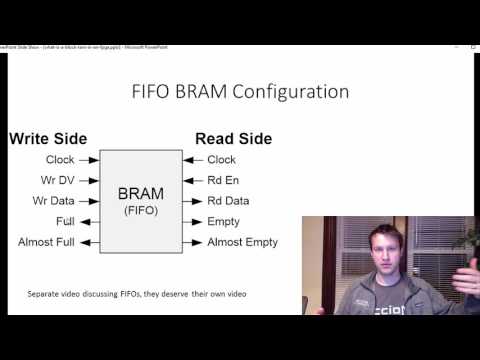

What is a Block RAM in an FPGA?Подробнее

FPGA Memory Registers and RAMПодробнее

FPGA BRAM Access ExampleПодробнее

ROM in quartus #quartus #rom #electronics #educationПодробнее

#7 Quartus IP modulesПодробнее

QuartusII Altera 2port RAM (32Byte)Подробнее

Securing FPGA IP and DataПодробнее

Memory Subsystem IP for Intel Agilex® 7 F-Series and I-SeriesПодробнее

using signal tap analyzer in quartus, to monitor signals live on fpgaПодробнее

Tutorial Creating RAM Memory Quartus II AlteraПодробнее

Agilex™ 5 FPGAs In-Action External Memory Interfaces IP Demo VideoПодробнее

Learn FPGA #20: SAVE Resources!!! (Distributed RAM vs. Block RAM) - TutorialПодробнее

Electronics: Why can't dual port RAM be read out using the Quartus In-System Memory Content Editor?Подробнее

using PLL ip in quartus, to get high frequency clockПодробнее

HLS Walkthrough Part 1: Creating an IP ComponentПодробнее