Programmable Logic Devices|| VLSI DESIGN STYLES||VLSI DESIGN

VLSI GUIDANCE 02Подробнее

Design & Implementation of Automatic Washing Machine Control System Using Verilog || Xilinx VivadoПодробнее

Design & Implementation of Automated Car Parking System Using Verilog|| Xilinx Vivado |Smart ParkingПодробнее

Design &Implementation of Snacks/Beverages Vending Machine Using Verilog HDL || Xilinx Vivado||FPGAПодробнее

what are corners in vlsi telugu||vlsi.vth.prakashПодробнее

Design & Implementation of an Advanced Traffic Light Controller Using Verilog HDL || Xilinx VivadoПодробнее

You Won't Believe The BEST VLSI Training Institute in HyderabadПодробнее

VLSI GUIDANCE 01Подробнее

Introduction to Low Power VLSI |Techniques to Reduce Power |Static Power &Dynamic Power DissipationПодробнее

Definition of Code Coverage, Types || Code Coverage Flow Using Cadence IES and ICCR Tools ||VerilogПодробнее

Lecture 01 : Introduction to VLSI DesignПодробнее

Gate Array layout style | VLSI Physical Design | VLSI Automation AlgorithmsПодробнее

Basics of VERILOG | Datatypes, Hardware Description Language, Reg, Wire, Tri, Net, Syntax | Class-1Подробнее

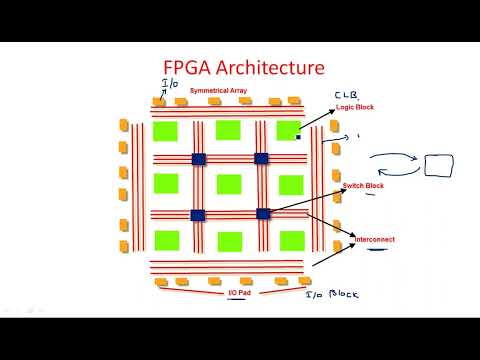

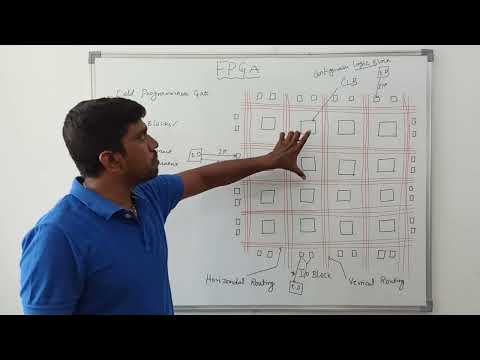

FPGA Architecture | Configurable Logic Block ( CLB ) | Part-1/2 | VLSI | Lec-75Подробнее

Field Programmable Gate Array in VLSI Design || Learn Thought || S Vijay MuruganПодробнее

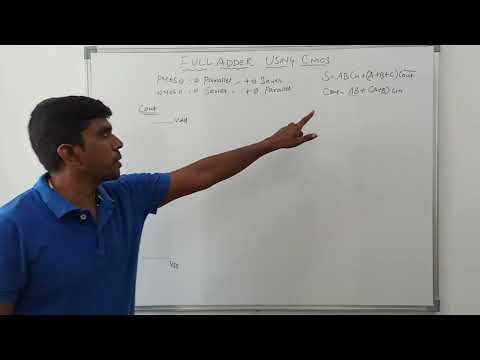

Full Adder Using CMOS Logic Design in VLSI Design || S Vijay Mururgan || Learn ThoughtПодробнее

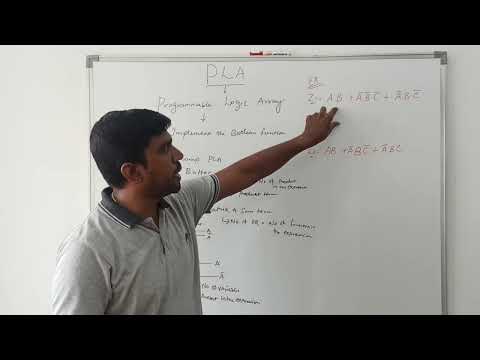

Programmable Logic Array (PLA) in VLSI Design || S Vijay Murugan || Learn ThoughtПодробнее

VLSI Testing &Testability||Fault Equivalence||Fault Collapsing||VLSI Testing||Design for TestabilityПодробнее

Design and Analysis of Approximate 4-2 Compressors for Multiplication || VLSI Latest Project IdeasПодробнее