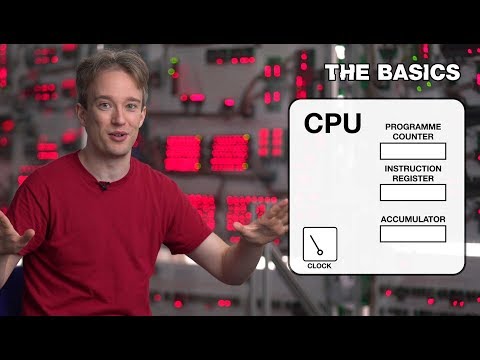

4. CPU, Memory and Instructions. Fetch, decode, execute... | Assembly, C on Bare-metal RISC-V

5. Instruction Set Architecture (ISA) | Assembly, C on Bare-metal RISC-VПодробнее

The Fetch-Execute Cycle: What's Your Computer Actually Doing?Подробнее

Fetch Decode Execute Cycle in more detailПодробнее

3. CPU Model. A Bunch of Registers! | Assembly, C on Bare-metal RISC-VПодробнее

Fetch decode execute cycleПодробнее

0. [Native: Linux] Lab Setup | Assembly, C on Bare-metal RISC-VПодробнее

![0. [Native: Linux] Lab Setup | Assembly, C on Bare-metal RISC-V](https://img.youtube.com/vi/-nQ5w2gtB1Q/0.jpg)

Assembly Programming with RISC-V: Part 1Подробнее

0. [Native: Mac OS] Lab Setup | Assembly, C on Bare-metal RISC-VПодробнее

![0. [Native: Mac OS] Lab Setup | Assembly, C on Bare-metal RISC-V](https://img.youtube.com/vi/KJtUWnJr254/0.jpg)

0. Lab Setup (Codespace) | Assembly, C on Bare-metal RISC-VПодробнее

CPU Fetch/Decode/Execute animationПодробнее

You Can Learn RISC-V Assembly in 10 Minutes | Getting Started RISC-V Assembly on Linux TutorialПодробнее

Fetch-Decode-Execute CycleПодробнее